ECE :: Digital Electronics

-

In a shift left register, shifting a bit by one bit means

-

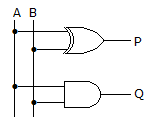

If A = B = 1, the outputs P and Q in the given figure are

-

Assertion (A): The access time of memory is lowest in the case of DRAM

Reason (R): DRAM uses refreshing cycle.

-

Assertion (A): Even if TTL gates and CMOS gates used in a realization have the same power supply of + 5 V, suitable circuit is needed to interconnect them

Reason (R): VOH, VOL, VIH and VIL of a TTL gave are respectively 2.4, 0.4, 2 and 0.8 V respectively. If supply voltage is + 5 V. VIL and VIH for CMOS gate for the supply voltage of + 5 V are 1.5 V and 3.5 V respectively.

-

Assertion (A): A PROM can be used as a synchronous counter

Reason (R): Each memory location in a PROM can be read synchronously.

Whatsapp

Whatsapp

Facebook

Facebook

.

.