ECE :: Digital Electronics

-

A 4 bit synchronous counter has flip flops having propagation delay of 50 ns each and AND gates having propagation delay of 20 ns each. The maximum frequency of clock pulses can be

-

A pulse train with a 1 MHz frequency is counted using a 1024 modulus ripple counter using JK flip flops. The maximum propagation delay for each flip-flop should be

-

What will be maximum input that can be converted for a 6 bit dual slope A/D converter uses a reference of -6v and a 1 MHz clock. It uses a fixed count of 40 (101000).

-

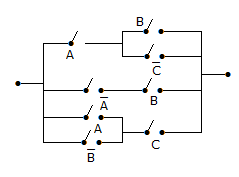

In the given figure shows a logic circuit. The minimum Boolean expression for this circuit is

-

If number of information bits is 11, the number of parity bits in Hamming code is

-

The number of digit 1 present in the binary representation of 3 x 512 + 7 x 64 + 5 x 8 + 3 is

Whatsapp

Whatsapp

Facebook

Facebook

.

. = 1 ms = 10 x delay of one flip flop. Therefore delay for one flip-flop = 0.1 ms.

= 1 ms = 10 x delay of one flip flop. Therefore delay for one flip-flop = 0.1 ms. .

.